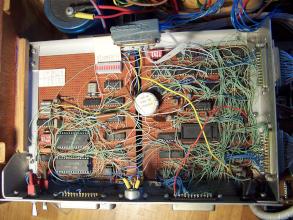

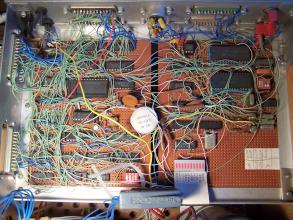

Main processor card (after upgrade to SIMM DRAM).

The Stallone (stand alone) computer was constructed in 1986 or thereabouts. It was based around a Motorola 68000 microprocessor and ran the Tripos Operating System that was widely in use at the University of Cambridge Computer Laboratory as part of the Cambridge Distributed System. However, Stallone was never directly connected to the Cambridge Ring; instead it was first booted using a serial download over a terminal concentrator connected to the Ring and after that it ran freestanding.

Stallone was almost exclusively programmed in BCPL.

The main memory was 2 megabytes of DRAM in two arrays. Each array had been part of a graphics workstation of some sort, but after the workstation was scrapped, I sawed out the DRAM part of the main PCB with a hacksaw and connected my own wires. Later on, the main memory was replaced with a pair of 1 megabyte SIMMs.

The I/O devices subsystem used the same wiring pinouts and protocols as the CHAOS computer and so was connected to CHAOS for initial development. The I/O consisted of a pair of UARTs, a parallel port, an EPROM programmer and a real-time clock. One serial port could be switched from MIDI to RS-232 physical connections.

The CHAOS floppy and hard disk subsystems could be used with Stallone. A 20 Megabyte, 5 inch hard disk was used most of the time.

Main processor card (after upgrade to SIMM DRAM).

Connection Panel. Connections for two serial ports, MIDI in and out,

one parallel port

and one CHAOS-style expansion port that would connect to the CHAOS floppy disk

drives.

Power supply. A linear supply, giving +5, +12 and -5 volts.

Back Panel, showing heatsink, mains inlet and ON/OFF power switch.

Right-hand bay: was fitted with various 5 inch floppies and hard disk drives over time.

Top views of I/O panel, showing UARTS, socket for programming EPROMs